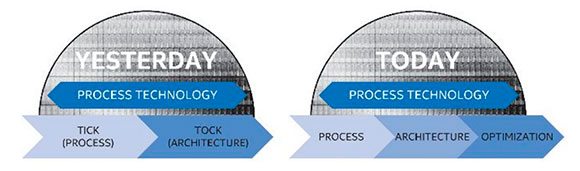

La strategia Tick-Tock ha cadenzato il successo e lo sviuppo tecnologico dei processori Intel nell’ultimo decennio, alternando la migrazione di un’architettura consolidata a un processo produttivo più raffinato (tick) con l’introduzione di una nuova architettura (tock). All’interno del documento 10-K/annual report, Intel ha esposto le difficoltà connesse con lo sviluppo dei nuovi processi litografici che hanno permesso di implementare la produzione a 14 nanometri e quelle relative allo sviluppo della prossima generazione di architetture a 10 nanometri.

Questi sono i motivi per cui la strategia Tick-Tock che prevedeva una alternanza di cicli su base annuale sarà trasformata in un processo a tre fasi con la possibilità di sfruttare una tecnologia produttiva su un arco di tempo più lungo; il nuovo processo sarà denominato Process-Architecture-Optimization (PAO) e sarà caratterizzato dalle due fasi tipiche della strategia Tick-Tock alle quali seguirà una fase di ottimizzazione dell’architettura (potremmo quindi chiamarlo anche Tick-Tock-Tack, ndr) così da allargare la finestra temporale per lo sviluppo e il perfezionamento dei processi produttivi di generazione successiva.

Il processo Tick-Tock (a sinistra) dove si alternano fasi di migrazione della tecnologia produttiva con quelle di sviluppo delle architetture. Il nuovo approccio PAO (a destra) che prevede tre fasi: migrazione a un processo produttivo di nuova generazione, introduzione di una nuova architettura e lo sviluppo di un’architettura ottimizzata basata su quella introdotta precedentemente.

Queste sono le parole estratte dal report divulgato da Intel e che delineano in modo preciso il cambio di strategia da parte della società di Santa Clara:

As part of our R&D efforts, we plan to introduce a new Intel Core microarchitecture for desktops, notebooks (including Ultrabook devices and 2 in 1 systems), and Intel Xeon processors on a regular cadence. We expect to lengthen the amount of time we will utilize our 14nm and our next generation 10nm process technologies, further optimizing our products and process technologies while meeting the yearly market cadence for product introductions.

Il passaggio al nuovo modello PAO è una conseguenza diretta delle difficoltà legate allo sviluppo delle nuove tecnologie di produzione del silicio e alla risoluzione dei problemi che emergono operando su scale sempre più piccole nella produzione dei transistor e delle architetture. Questi fattori sono emersi in modo dominante durante lo sviluppo della tecnologia FinFET a 14 nanometri, con Intel che sarebbe stata costretta a ridurre in modo eccessivo la finestra temporale di presenza sul mercato di una architettura per restare fedele alla cadenza ciclica di un anno tra una fase di tick e quella successiva di tock. Il maggior tempo disponibile per sfruttare un processo produttivo permetterà a Intel anche di rientrare con più facilità dei costi di ricerca sostenuti per lo sviluppo delle tecnologie produttive più avanzate e per l’aggiornamento degli impianti di produzione.